# 行政院國家科學委員會專題研究計畫 成果報告

## 動態可重組態現場可程式系統晶片電路放置問題之研究

計畫類別: 個別型計畫

計畫編號: NSC91-2215-E-343-001-

執行期間: 91年08月01日至92年07月31日

執行單位: 南華大學資訊管理學系

計畫主持人:吳光閔

計畫參與人員: 李建圖、吳建億、盧奎佑、厲彥廷

報告類型: 精簡報告

處理方式: 本計畫可公開查詢

中 華 民 國 92 年 10 月 31 日

## 行政院國家科學委員會補助專題研究計畫成果報告

# 動態可重組態現場可程式系統晶片電路 放置問題之研究

計畫類別: 個別型計畫 整合型計畫

計畫編號: NSC91-2215-E-343-001

執行期間:91年08月01日至92年07月31日

計畫主持人:吳光閔 副教授

共同主持人:

計畫參與人員:李建圖、吳建億、盧奎佑、厲彥廷

執行單位:南華大學資訊管理學系

中 華 民 國 92年 10月 31日

# 動態可重組態現場可程式系統晶片電路放置問題 之研究

計畫編號: NSC91-2215-E-343-001 執行期間: 91年8月1日 至 92年7月31日

主持人:吳光閔副教授 南華大學資訊管理學系

計畫參與人員:李建圖、吳建億、盧奎佑、厲彥廷 南華大學資訊管理學

系

### 一、英文摘要

With ever increasing circuit complexity, the logic integrated into a single FPGA chip is growing dramatically. Consequently, like ASIC designs, FPGA designs are becoming systems-on-a-chip, integrating together the entire system's functionality. Dynamically Reconfigurable FPGAs (DRFPGAs) for reconfigurable computing, a promising alternative for improving logic efficiency by dynamically re-using hardware, has become an important research topic in field-programmable systems-on-chips.

In this plan, we introduce a new placement problem motivated by the Dynamically Reconfigurable FPGA (DRFPGA) architectures. Due to the reuse of logic and interconnect, the placement problem for DRFPGAs is quite different from the traditional one. For the DRFPGA placement, we develop a three-stage scheme of partitioning, initial placement generation, and placement refinement to solve the new placement problem for DRFPGAs.

Keywords: FPGA, DRFPGA, placement, reconfigurable computing.

### 二、中文摘要

隨著電路及晶片複雜度的與日俱增, FPGA 的設計亦如 ASIC 設計般趨向系統整合晶片發展。

隨著電路及晶片複雜度的與日俱增,FPGA的設計亦如ASIC設計般趨向系統整合晶片發展。動態可重組態現場可程式閘陣列(DRFPGAS)可藉由動態重新使用FPGA硬體來增進邏輯效能,因此,其為當今現場可程式系統整合晶片之重要研究主題。

在本計畫中,我們介紹了一個新的放置(placement)問題,其靈感來自於動態可重組態現場可程式閘陣列的結構,由於此結構中電路連線和邏輯元件可在問時序間重新使用,因此,動態可重組態現場可程式閘陣列之放置問題與傳統 ASIC放置問題截然不同。對於此一新的放置問題,本計畫已發展一個三階段(three-stage)的方法來處理它,其包含:在第一階段,我們將嘗試發展一個快速有效的分割方法(partitioning),在第二階段,我們將找出不錯初始放置方法,並在第三階段做更好的調整。

關鍵詞:現場可程式閘陣列、動態可 重組態現場可程式閘陣列、放置問題、重 新組態計算。

#### 三、背景和目的

#### (一) 背景

動態可重組態現場可程式閘陣列 (DRFPGA)藉由動態重新使用 FPGA 硬體而 增進了邏輯效能。在當下,用來處理可重 組態計算的 DRFPGA 引發了日趨強烈的重 視。藉著運用 DRFPGA, 一個規模龐大的設計可被分割為多個階段, 在不同的時間中, 分享相同的小型實體設備。有幾個不同的 架構被提出:例如 Xilinx architecture[18]、 Virtual Element Gate Array[12]、 Dynamically Programmable Gate Array[3, 8]、Dharma[1]等等。藉著修改在晶片上的靜態記憶體(SRAM)的 bit 數, 這些模組均允許邏輯模組與線段的動態重新使用。

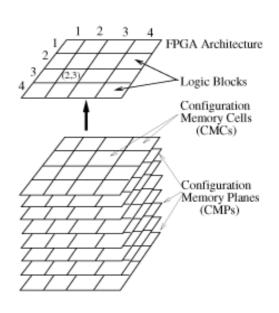

圖一展示了 Xilinx DRFPGA 配置模組 [18],這個動態可重組態現場可程式閘陣 列,藉由將一個大規模的設計,分割成多 個組態,進而進行模擬。線路設計結構可 以被分割為多個階段,並儲存在結構記憶 平面中。在任何時間下, DRFPGA 可以維持 只有一個在運作中的組態,將他載入到 FPAG 的邏輯陣列中,加以模擬,模擬完 成後將其結果儲存在靜態記憶體中,再提 供給下一個線路組態使用,如此,一個接 一個的將所有的線路組態執行完成。在此 過程中,每個線路組態被執行的過程稱作 微週期, 而通過所有組態微週期的過程稱 之為使用者週期。一個微週期開始時,會 把先前的迷你週期的所有結構性的邏輯 區塊之結果,儲存在迷你暫存器中,然後 一個新的架構被裝載到活躍的架構記憶 體裡。裝載的過程稱為快閃架構變換。

由於邏輯的再利用和相互連接,對DRFPGAs的放置問題非常不同於傳統的放置問題。不像傳統 FPGAs 一樣,節點實施的次序必須在 DRFPGA 中滿足優先權的約束。我們在 DRFPGA 中提出一個節點的壽命如同階層持續的期間當節點最後被使用時所分配的階層。在它的壽命期間節點最後被如這些節點的壽命週期沒有重疊的話,許多的節點值可以被儲存在一個相同的迷你暫存器裡。相對地,如果有兩個結合性或者佔有節點,在不同記憶體項目和他們的壽命週期重複部分方面放在相同的位置裡,則他們的結果不能在迷你暫存器裡

儲存相同的記憶體空間。除此之外,其相同位置中的壽命週期重複的節點數目,不能超過迷你記憶體的容量---迷你暫存器容量的約束。傳統上,都以電線長度或電線使用段量作為路徑規劃成本的計算規則,例如,[1,2,5,6,7,9,10,12,13,14,16,18]。這個規則通常包含在一般的佈線評估案中,例如:semi-perimeter, Steiner tree, minimum spanning tree等。然而由於優先權與迷你暫存器的容量限制,這些規則對於DRFPGA配置並不適用。

圖一: Xi l inx動態可重組態現場可程式 閘陣列組態模式

#### (二)目的

對於DRFPGA的放置問題,我們發展了新的評估標準,此標準能同時考量:「連線長度」、「微記憶體的使用率」和「耗電量」,並且能滿足DRFPGA的時序限制。根據上述的評估標準的考量和DRFPGA的時序限制我們發展了一個三階段式的演算法:第一階段先提出一DRFPGA的分割方法、第二階段我們提出一個快速的放置方法來將設計線路很快速安排到一不錯的解。最後在第三階段我們利用一重複精練的方式來解此一新的DRFPGAs放置問題

#### 四、研究方法

在這份計畫報告中,我們先提出一 DRFPGA的分割方法來處理多階優先限制 分割之問題。首先,我們對分割目標與限 制這些較容易轉換為整合線性程式數學 描述的部分,進行數學描述。與現存可同 時考量到優先限制與只在一些局部階段 內的切割大小之大部分方法不同,以整合 線性程式為基礎的方法可以同時地考慮 到所有階段,因此,它對所給定的目標之 最佳化擁有一個更具總體性的透視。

第二階段我們提出一個快速的放置方法來將設計線路很快速安排到一不錯的解。最後在第三階段我們利用一重複精練的方式來解此一新的DRFPGAs放置問題。

最後我們利用廣泛實驗法來驗證我們所 提出之演算法:利用我們所提出之放置演 算法作廣泛的實驗以觀察各「連線長 度」、「微記憶體的使用率」和「耗電量」 的情況。

#### 五、成果(Publications)

- 1. Guang-Ming Wu, J.-M. Lin, and Y.-W. Chang, "Precedence-constrained placement for dynamically reconfigurable FPGAs," in ACM Trans. on Design Automation of Electronic Systems (TODAES), Vol. 7, No. 4, October 2002.

- G.-M. Wu, T.-C. M. Chao, and Y.-W. Chang., ``A Clustering- and Probability-Based Approach for Time-Multiplexed FPGA Partitioning," revised in IEEE Transactions on VLSI.

### 六、參考文獻

[1]. M. J. Alexander, J. P. Cohoon, J. L. Ganley, G. Robins, "Performance-Oriented Placement and Routing for Field-Programmable Gate Arrays,"

- Proc.~EuroDAC, pp. 80--85, 1995.

- [2]. V. Betz, J. Rose, and A. Marquardt, Architecture and CAD for Deep-Submicron FPGAs, Kluwer Academic Pub., 1999.

- [3]. N. B. Bhat, and K. Chaudhary, and E. S. Hah, ``Performance-oriented fully routable dynamic architecture for a field programmable logic device," Memmorandum No. UCB/RELM93/42, University of California, Berkeley, 1993.

- [4]. J. Brown, et al. ``DELTA: Prototype for a first-generation dynamically programmable gate array," *Transit Note* 112, MIT, 1995.

- [5]. S. Brown, G. Lemieux, and M. Khellah, "Segmented Routing for Speed-Performance and Routability in Field-Programmable Gate Arrays", Journal of VLSI Design, 4(4), pp. 275--291, 1996.

- [6]. Y. W. Chang, S. Thakur, K.Zhu, and D. F. Wang, ``A new global routing algorithm for FPGAs," *Proc.~of IEEE/ACM International Conference on Computer-Aided-Design*, pp. 380--385, 1994.

- [7]. C. D. Chen, Y. S. Lee, C. H. Wu, and Y. L. Lin, ``TRACER-fpga: a router for RAM-based FPGA's," *IEEE Trans. on Computer-Aided Design*, vol. 14, no. 3, pp. 371--374, March 1995.

- [8]. A. DeHou, "DPGA-coupled microprocessors: Commodity ICs for the early 21st century," in *IEEE Workshop on FPGAs for Custom computing Machines*, 1994.

- [9]. C. Ebeling, L. McMurchie, S. A. Hauck,

- and S. Burns, "Placement and routing tools for the triptych FPGA," *IEEE Trans.~on VLSI Systems*, pp. 473--482, December 1995.

- [10]. J. Frankle, "Iterative and adaptive Slack Allocation for Performance-Driven Layout and FPGA Routing," *Proc.~of* 29th Design Automatic Conference, pp. 536-542, 1992.

- [11]. D. Jones and D. M. Lewis, "A time-multiplexed FPGA architecture for logic emulation, " in *IEEE Custom Integrated Circuits Conference*, 1995.

- [12]. Y. S. Lee and C. H. Wu, "A Performance and Routability Driven Router for FPGA's Considering Path Delay," *Proc.~of 32th Design Automatic Conference*, pp. 557--561, 1995.

- [13]. S. K. Nag and R. A. Rutenbar, "Performance-driven simultaneous placement and routing for FPGA's," *IEEE Trans. on Computer-Aided Design*, Vol. 17, No. 6, pp. 499--518, June 1998.

- [14]. N. Togawa, M. Sato, and T. Ohtsuki, "Maple: A Simultaneous Technology Mapping Placement, and Global Routing Algorithm for Field-Programmable Gate Arrays," *IEEE/ACM International Conference on Computer-Aided-Design*, pp.156--163, 1994.

- [15]. S. Trimberger, ``A Time-Multiplexed FPGA," in *IEEE Workshop on FPGAs for Custom computing Machines*, pp. 22--28, 1997.

- [16]. Y.-L. Wu and M. Marek-Sadowska, "Orthogonal Greedy Coupling--A New Optimization Approach to 2-D FPGA Routing," *Proc.~of Design Automation*

- Conference, June 1995.

- [17]. Xilinx Inc., The Programmable Logic Data Book, 1996.

- [18]. K. Zhu, Y.-W. Chang, and D. F. Wong, "Timing-driven routing for symmetrical-array-based FPGAs," Proc.~of International Conference on Computer Design, Austin, TX, October 1998.

- [19]. C. Y. Hitchcock III and D. E. Thomas, "A Method of Automatic Data Path Synthesis," in proc. 20th Design Automationh Conf., pp. 484-488, 1983.

- [20]. C. M. Fidducia and R. M. Mattheyses,

"A linear-time heuristic for improving

network partitions", *Proc.~of 19th Design Automatic Conference*,

pp.175--181, 1982.